Автор: Денис Аветисян

Исследователи предлагают методику для точного определения вклада отдельных микроархитектурных особенностей в общую производительность системы.

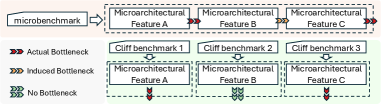

Представлен метод Microarchitecture Cliffs для создания эталонных тестов, изолирующих и атрибутирующих различия в производительности отдельным микроархитектурным компонентам.

Несмотря на широкое использование архитектурных симуляторов для оптимизации микроархитектуры, их точность часто ограничена расхождениями с реальным аппаратным обеспечением. В данной работе, посвященной ‘Benchmarking for Single Feature Attribution with Microarchitecture Cliffs’, предложен новый метод генерации тестов — Microarchitecture Cliffs, позволяющий выявлять и локализовать причины этих расхождений до отдельных микроархитектурных особенностей. Применение данного подхода к симулятору gem5 (XS-GEM5) и открытому процессору XiangShan позволило снизить ошибку производительности с 59.2% до 1.4%, значительно повысив точность моделирования. Какие перспективы открывает данный метод для автоматизированной калибровки и оптимизации будущих архитектур процессоров?

Неизбежность Расхождений: Вызов Точности в Архитектурном Моделировании

Современная разработка чипов в значительной степени опирается на архитектурные симуляторы для исследования производительности, однако получение точных результатов представляется удивительно сложной задачей. Эти симуляторы позволяют инженерам виртуально протестировать различные конструктивные решения, прежде чем приступать к дорогостоящему и длительному процессу физической реализации. Несмотря на их широкое использование, существует ощутимый разрыв между поведением, наблюдаемым в симуляции, и фактической производительностью готового чипа. Это связано с тем, что симуляторы, по своей природе, являются упрощением реальности, и не всегда способны точно отразить все нюансы и тонкости, возникающие в процессе работы физического устройства. Несмотря на постоянное совершенствование алгоритмов и моделей, достижение полной достоверности симуляций остается сложной научной и инженерной проблемой, требующей постоянных усилий и инноваций.

Существует фундаментальное несоответствие — так называемый “Вызов точности” — между смоделированным поведением и финальной RTL-реализацией, что представляет серьезную проблему в процессе разработки чипов. Данное расхождение возникает из-за сложностей точного моделирования реальных физических эффектов и неизбежных упрощений, вносимых в симуляции для обеспечения приемлемой скорости работы. В результате, характеристики, успешно продемонстрированные в симуляторе, могут существенно отличаться от реальной производительности чипа после его изготовления, что потенциально приводит к скрытым дефектам, снижению производительности и увеличению затрат на исправление ошибок. Решение этой проблемы требует постоянного совершенствования методов моделирования и разработки новых подходов к верификации, чтобы гарантировать соответствие смоделированного поведения реальному функционированию процессора.

Несоответствие между результатами архитектурного моделирования и реальной работой микросхемы обусловлено фундаментальной сложностью точного воспроизведения всех физических эффектов, возникающих в процессе работы. Моделирование неизбежно использует абстракции, упрощая реальность для достижения приемлемой скорости расчетов. Однако, эти упрощения могут приводить к игнорированию важных нюансов, таких как задержки распространения сигналов, влияние температуры, вариации параметров технологического процесса и электромагнитные помехи. Чем выше уровень абстракции, тем больше потенциальная ошибка. Таким образом, несмотря на все достижения в области моделирования, полное и точное предсказание поведения реального чипа остается сложной задачей, требующей постоянного совершенствования методов и алгоритмов моделирования.

Преодоление проблемы точности моделирования имеет решающее значение для оптимизации циклов проектирования и обеспечения высокой производительности будущих процессоров. Неточности в архитектурном моделировании могут приводить к скрытым дефектам, которые проявляются только на этапе реализации, что влечет за собой дорогостоящие и трудоемкие исправления. Повышение точности симуляторов позволяет разработчикам более эффективно исследовать различные архитектурные решения, выявлять узкие места и оптимизировать производительность на ранних этапах проектирования. Это, в свою очередь, сокращает время выхода продуктов на рынок и снижает риски, связанные с дорогостоящими ошибками в финальной реализации. В конечном итоге, инвестиции в повышение точности моделирования являются ключевым фактором для поддержания инноваций и конкурентоспособности в сфере разработки микропроцессоров.

Калибровка Модели: Устранение Разрыва Между Симуляцией и Реальностью

Эффективная калибровка модели является основополагающим этапом в точном архитектурном моделировании, направленным на минимизацию проблемы достоверности (Fidelity Challenge). Недостаточная калибровка приводит к значительным расхождениям между результатами симуляции и реальным поведением проектируемой системы, что может привести к неверным проектным решениям. Калибровка включает в себя настройку параметров модели таким образом, чтобы ее выходные данные максимально соответствовали наблюдаемым данным или известным характеристикам реальной архитектуры. Оценка качества калибровки обычно осуществляется путем сравнения ключевых показателей производительности, таких как задержка, пропускная способность и энергопотребление, полученных в симуляции и измеренных в реальной системе или в эталонных реализациях.

Существуют два основных подхода к калибровке симуляторов: калибровка, основанная на спецификациях (Specification-Driven), и калибровка, основанная на поведении (Behavior-Driven). Specification-Driven калибровка предполагает настройку параметров симулятора в соответствии с известными техническими характеристиками и документацией на моделируемое оборудование или систему. В свою очередь, Behavior-Driven калибровка фокусируется на настройке параметров симулятора таким образом, чтобы его выходные данные максимально соответствовали наблюдаемому поведению реальной системы, полученному в результате измерений или экспериментов. Оба подхода обладают своими преимуществами и недостатками, и их комбинированное использование позволяет добиться наиболее точной и достоверной симуляции, учитывая как априорные знания о системе, так и эмпирические данные.

Комбинированный подход к калибровке модели, включающий как спецификацию (Specification-Driven), так и поведенческую (Behavior-Driven) калибровку, обеспечивает более полное выявление и исправление расхождений в модели симуляции. Спецификационная калибровка позволяет проверить соответствие модели заданным параметрам и требованиям, в то время как поведенческая калибровка фокусируется на сопоставлении выходных данных модели с реальным поведением системы. Использование обеих методик совместно позволяет не только выявить ошибки, связанные с неправильными параметрами, но и обнаружить несоответствия в логике модели, что приводит к повышению точности и достоверности результатов симуляции. Данная стратегия особенно эффективна при моделировании сложных архитектур, где взаимодействие компонентов может приводить к нелинейным эффектам и трудноуловимым ошибкам.

Выявление Узких Мест: Анализ Микроархитектурных Пределов

Микротестирование предоставляет детальный подход к исследованию конкретных микроархитектурных компонентов, таких как очередь загрузки (Load Queue), кэш первого уровня (DCache) и буфер переупорядочения (ROB). В отличие от комплексных бенчмарков, микротесты позволяют изолированно оценивать производительность отдельных элементов конвейера процессора. Это достигается путем создания небольших программ, специально разработанных для интенсивного использования целевого компонента, что позволяет точно определить его пропускную способность, задержки и потенциальные узкие места. Анализ результатов микротестов позволяет выявить, какие конкретно микроархитектурные особенности влияют на общую производительность системы и требуют оптимизации.

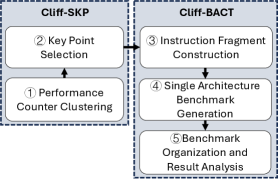

Методология “Микроархитектурные Пределы” (Microarchitecture Cliffs) предполагает систематическое выявление причин расхождений в производительности путем атрибуции этих расхождений к отдельным компонентам микроархитектуры. Этот процесс включает в себя последовательное ограничение ресурсов, таких как очередь загрузки, кэш данных или буфер переупорядочивания (ROB), и измерение влияния этого ограничения на общую производительность. Обнаруживая компонент, который первым становится узким местом при уменьшении доступных ресурсов, можно точно определить критическую область, ограничивающую производительность. Такой подход позволяет выявить скрытые узкие места, которые не проявляются при традиционном анализе производительности, и целенаправленно оптимизировать эти компоненты для достижения максимальной эффективности.

Для точного измерения влияния отдельных компонентов микроархитектуры на производительность исследователи используют счетчики производительности (Performance Counters). Эти счетчики предоставляют данные о частоте использования и эффективности работы таких элементов, как очередь загрузки, кэш данных и буфер переупорядочения (ROB). Анализ данных счетчиков позволяет выявить узкие места и определить, какие компоненты вносят наибольший вклад в снижение производительности. На основе этих данных возможно целенаправленное проведение оптимизации, направленной на улучшение работы критически важных элементов и повышение общей эффективности системы. Счетчики производительности позволяют количественно оценить влияние изменений в коде или аппаратной части на работу конкретных компонентов.

Детальный анализ с использованием методологии “Microarchitecture Cliffs” позволяет точно определить компоненты микроархитектуры, оказывающие наибольшее влияние на производительность. Это обеспечивает целенаправленное применение усилий по калибровке и оптимизации, исключая затраты ресурсов на некритичные области. В результате, эффективность калибровки максимизируется, поскольку корректировки вносятся именно в те компоненты, которые существенно влияют на общую производительность системы, что приводит к наиболее заметному улучшению ключевых показателей.

Проверка Симуляции: XS-RTL как Эталон Истины

Для валидации откалиброванного симулятора необходимо сопоставить его прогнозы с функциональной реализацией архитектуры — XS-RTL. XS-RTL выступает в качестве «золотого стандарта», обеспечивая точное и проверенное исполнение инструкций. Сравнение результатов симуляции с результатами, полученными на XS-RTL, позволяет оценить точность моделирования и выявить потенциальные расхождения. Использование XS-RTL в качестве эталона гарантирует, что любые улучшения в симуляторе действительно отражают повышение точности прогнозирования производительности, а не просто изменения в реализации симулятора.

Использование стандартизированных бенчмарков, таких как SPEC CPU2006/2017, обеспечивает объективное сравнение метрик производительности. Эти наборы тестов включают в себя широкий спектр приложений, представляющих различные вычислительные нагрузки, что позволяет оценить производительность архитектуры в реалистичных сценариях. Стандартизация гарантирует воспроизводимость результатов и позволяет сравнивать производительность различных систем и конфигураций без влияния субъективных факторов или специфических настроек. Объективность сравнения критически важна для валидации симуляторов и оценки точности моделирования архитектуры.

Использование Verilator в качестве рабочей нагрузки как для XS-GEM5, так и для XS-RTL обеспечивает согласованность процесса оценки. Verilator является симулятором RTL (Register-Transfer Level) на основе C++, который позволяет быстро и эффективно моделировать поведение цифровых схем. Применение единой рабочей нагрузки — Verilator — для обеих платформ — эмулятора XS-GEM5 и эталонной реализации XS-RTL — гарантирует, что любые наблюдаемые различия в производительности или точности связаны именно с особенностями моделирования в XS-GEM5, а не с различиями в используемых тестовых программах или параметрах симуляции. Это критически важно для объективного сравнения и валидации точности калиброванного симулятора.

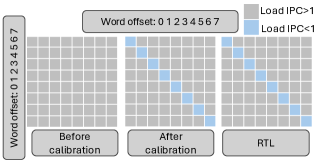

Применение данной методологии позволило добиться снижения абсолютной ошибки в оценке производительности на стандартных бенчмарках SPEC CPU2006 на 7.6%, SPECfp2006 на 15.1%, SPECint2017 на 15.1% и SPECfp2017 на 21.0%. Полученные результаты демонстрируют значительное повышение точности моделирования и ее соответствие фактической производительности архитектуры, что подтверждается объективными данными, полученными при сравнении с эталонной реализацией XS-RTL.

Калибровка значительно повысила точность оценки производительности Store Set, снизив относительную ошибку с 48.86% до 0.83%. Кроме того, при использовании набора тестов Cliff, общая ошибка составила всего 1.8%. Эти результаты демонстрируют высокую эффективность методики оценки и подтверждают возможность получения точных данных о производительности архитектуры после проведения калибровки.

Исследование, представленное в данной работе, демонстрирует закономерность, согласно которой попытки оптимизации отдельных микроархитектурных особенностей неизбежно приводят к возникновению новых, неожиданных зависимостей в системе. Методология Microarchitecture Cliffs, выделяющая влияние каждой особенности, лишь подтверждает эту тенденцию. Как однажды заметил Давид Гильберт: «Вся математика скрыта в логике, а вся логика — в математике». Аналогично, в архитектуре вычислительных систем, каждая деталь, казалось бы, изолированная, неразрывно связана с целостностью и уязвимостью всей структуры. Оптимизация одной части может создать «обрыв» в производительности, демонстрируя, что система не строится, а скорее вырастает из сложной сети взаимосвязей.

Что дальше?

Представленная методология “Микроархитектурных обрывов” выявляет не просто цифры производительности, но и те незримые шрамы, которые каждый архитектурный выбор оставляет на будущем системы. Однако, стоит признать, что калибровка микроархитектуры — это не поиск абсолютной истины, а скорее картографирование неизбежных компромиссов. Бенчмарки, даже столь тщательно сконструированные, всегда лишь приближение к реальности, запечатлевающее лишь момент истины, а не саму её суть.

Следующим шагом видится не столько усложнение самих бенчмарков, сколько разработка инструментов, способных предсказывать появление этих “обрывов” ещё на этапе проектирования. Система, способная моделировать не только среднюю производительность, но и вероятность возникновения узких мест, стала бы настоящим пророчеством о будущих сбоях. Ирония в том, что такая система сама станет сложной и подверженной ошибкам, но это — цена знания.

В конечном итоге, задача не в том, чтобы построить идеальную систему, а в том, чтобы научиться выращивать её, принимая неизбежные недостатки как часть её природы. Логирование станет исповедью, а каждый алерт — откровением. И когда спросят, когда закончится отладка, ответ будет прост: никогда — просто мы перестанем смотреть.

Оригинал статьи: https://arxiv.org/pdf/2602.11580.pdf

Связаться с автором: https://www.linkedin.com/in/avetisyan/

Смотрите также:

- Внимание на границе: почему трансформеры нуждаются в «поглотителях»

- Внимание в сети: Новый подход к ускорению больших языковых моделей

- Химический синтез под контролем искусственного интеллекта: новые горизонты

- Искусственный нос будущего: как квантовая механика и машинное обучение распознают запахи

- Когда большая языковая модель молчит: как избежать галлюцинаций при ответе на вопросы?

- Физика под контролем: Как «научить» модели понимать мир

- Пространственная Архитектура для Эффективного Ускорения Нейросетей

- Квантовые вычисления: Распределенная архитектура и моделирование схем

- Искусственный интеллект нового поколения: фокус на специализированные модели

- Масштабная Интерпретация: Новый Взгляд на Надежность Нейросетей

2026-02-14 23:07